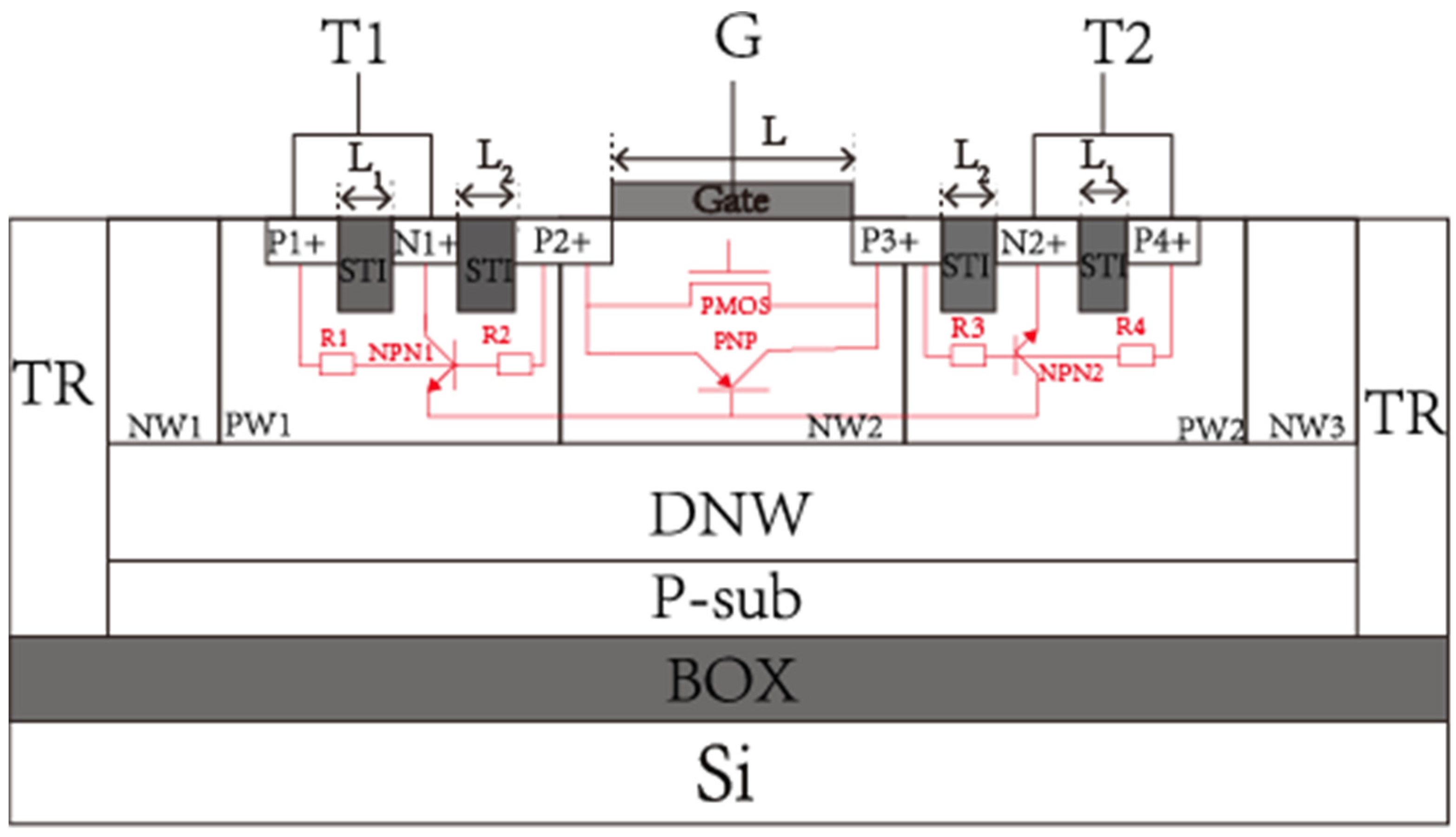

Electronics | Free Full-Text | The ESD Characteristics of a pMOS-Triggered Bidirectional SCR in SOI BCD Technology

Electronics | Free Full-Text | The ESD Characteristics of a pMOS-Triggered Bidirectional SCR in SOI BCD Technology

Snapback breakdown ESD device based on zener diodes on silicon-on-insulator technology - ScienceDirect

High Trigger Current NPN Transistor With Excellent Double-Snapback Performance for High-Voltage Output ESD Protection | Semantic Scholar

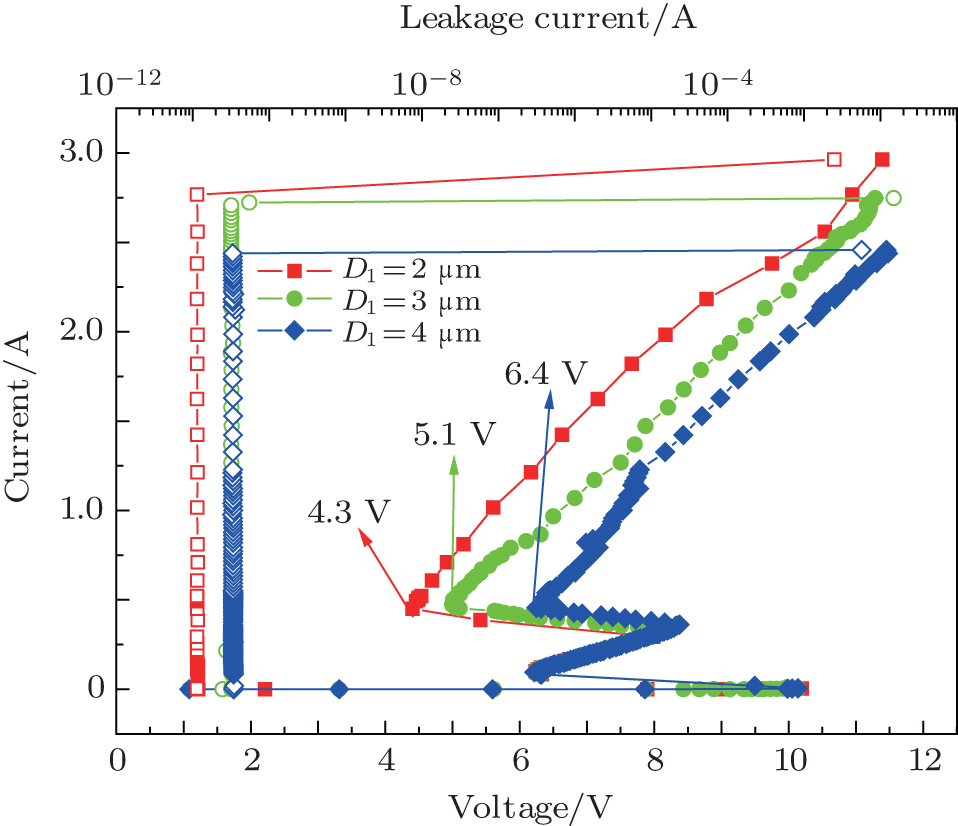

Measured IV-curve and simplified model for ESD-protection elements with... | Download Scientific Diagram

Mix‐mode forward‐biased diode with low clamping voltage for robust ESD applications - Qi - 2020 - Electronics Letters - Wiley Online Library

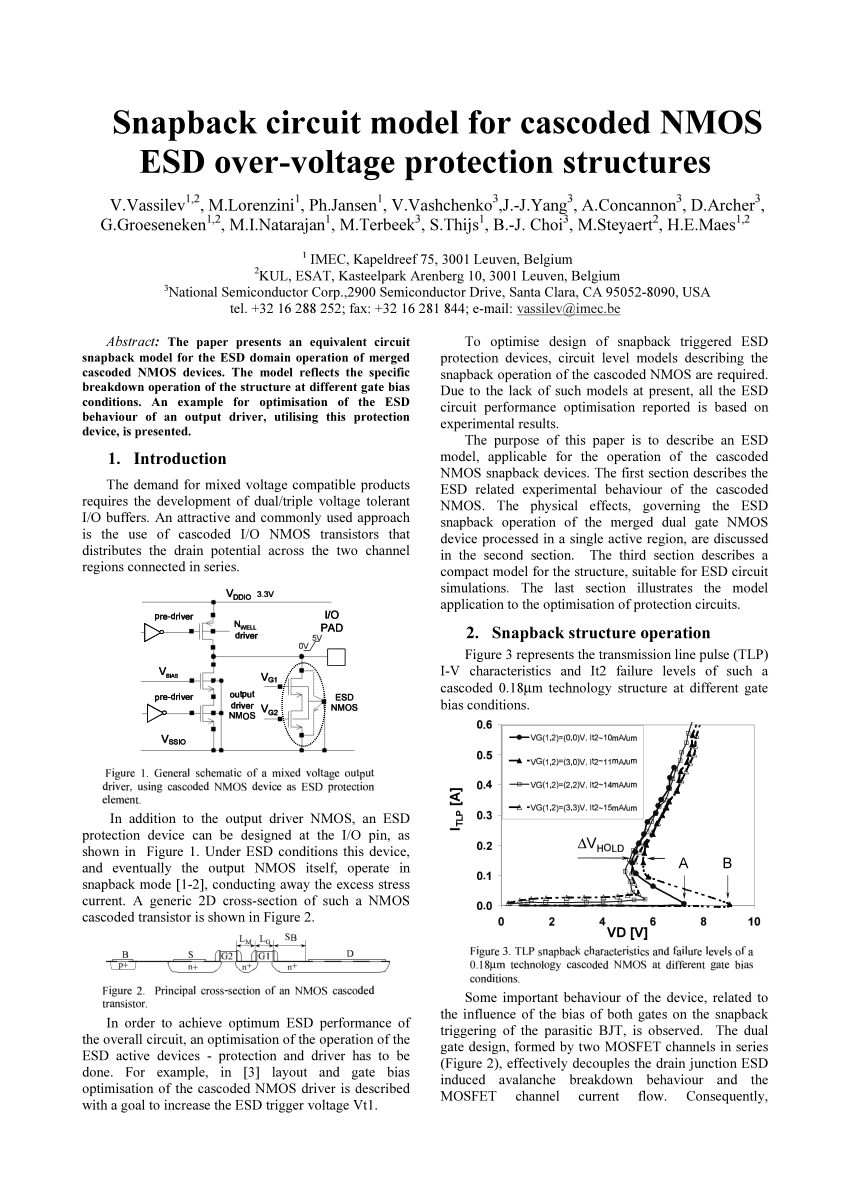

Modeling MOS snapback and parasitic bipolar action for circuit-level ESD and high current simulations | Semantic Scholar